2024-02-26 14:56:20

的数字输出引脚分为开漏(OD, Open Drain)和推挽(Push-Pull)结构。开漏结构可以进行并联实现或逻辑,在后级芯片识别逻辑与本身耐压范围内可以拉到系统的任何电压,使用十分灵活。芯片上常见的OD结构输出常见于ry),电压监控复位芯片的Reset 和 PFO(Power Fail)等,所有漏开输出都需要使用外部上拉或下拉

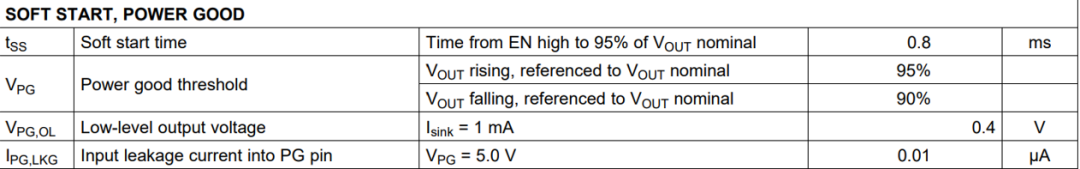

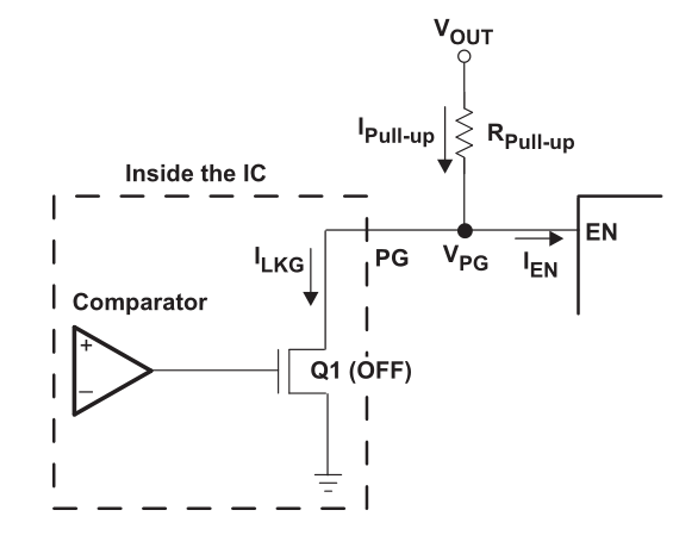

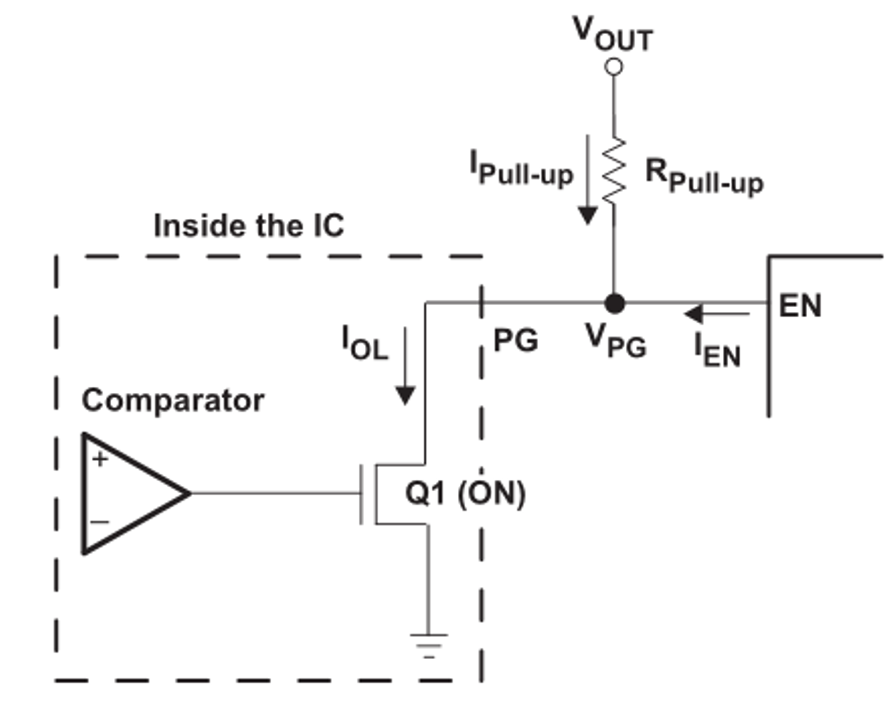

芯片发出动作信号驱动低输出时则需要上拉电阻。例如TPS62085,具有PG输出龙8long8唯一官方网站,如果芯片的输出电压不处于调节状态,它将驱动低电平。因此,PG需要一个上拉电阻,当芯片允许PG引脚浮动时,它将PG引脚拉高,表明电源良好,使能下级芯片,保证系统正常运行。

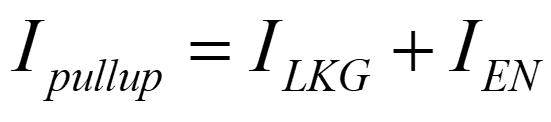

当Q1关闭龙8long8唯一官方网站,ILKG与IEN 在上拉电阻上产生压降,因此到EN上电压会有降低,为了满足下级芯片EN逻辑高电平。

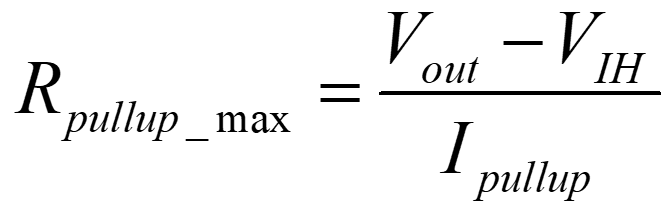

如果选择更大的电阻会导致RPull-up上的电压降更大,这将导致VPG低于VIH的最小值。后级芯片无法识别PG电压为逻辑高。

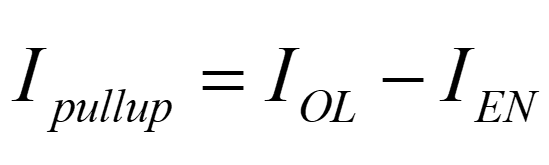

Q1开通导通电阻Rdson使得PG电压高于0V。当Q1接通时,PG电压必须足够低,以shutdown后级芯片。IOL在数据手册作为PG输出低电平 VOL的测试电流。VOL在IOL下不会超过其规定的最大电压。long8唯一官方网站可以使用达到指定的绝对最大PG吸收电流的电流,但它们可能产生高于其指定最大值的VOL。IC的测试电流和后级EN输入的漏电流相减为流过上拉电阻的电流。

上拉电阻两端的电压等于Vout减去VPG。VPG此时的最大值VOL=0.4V。电阻的最小值需要保证Q1中流过电流小于IOL。大于IOL会导致Q1压降无法保证低于0.4V。为了确保符合测试条件,保证VOL最大不超过0.4V,可通过下式计算出最小上拉阻力。

实际数据手册会给出建议上拉/下拉的电阻阻值,而且一般电阻可选范围较宽(1k~500kΩ),使用建议值是最方便可以保证系统正常工作。

文章出处:【微信号:gh_3a15b8772f73,微信公众号:硬件工程师炼成之路】欢迎添加关注!文章转载请注明出处。

? /

功能实现原理详解 /

来路,还恳请各位帮忙引导~~决定因子有那些.值得大家深入,问过公司好多同事,都说不出所以然.网友1:上拉或

的接线方法及作用介绍 /

的出发点在正常工作或单一故障状态下,管脚均不应出现不定状态从功耗角度考虑,在长时间的管脚等待状态下,

在电路设计中的应用 /

应用很简单吗? /

【昉·星光 2 高性能RISC-V单板计算机体验】以容器的方式安装 HomeAssistant

地址:宁波市鄞州区中钟公庙街道天童北路1393号322室 Copyright © 2012-2023龙8-long8唯一官方网站 版权所有

ICP备案编号:辽ICP备14525020号