2024-03-30 22:12:23

晶体管作为现代信息技术产业的强大引擎,一直以来都在推动着计算机、通信、娱乐和科学领域的创新和发展。自20世纪中叶诞生以来,晶体管不断演进,从最早的晶体管到如今的金属氧化物半导体场效应晶体管(MOSFET),其性能和功能也不断提升。然而,随着器件尺寸的不断缩小,晶体管面临着许多技术挑战和限制,为了突破这些限制,我们必须从根本上重新思考晶体管的未来。

鉴于此,近日来自美国加州圣芭芭拉分校的Kaustav Banerjee教授领导的研究团队在Nature上以The future transistors为题发表展望(Perspective)文章,总结了晶体管的发展历程,分析了晶体管的工作机制,并深入展望了未来晶体管的发展方向。

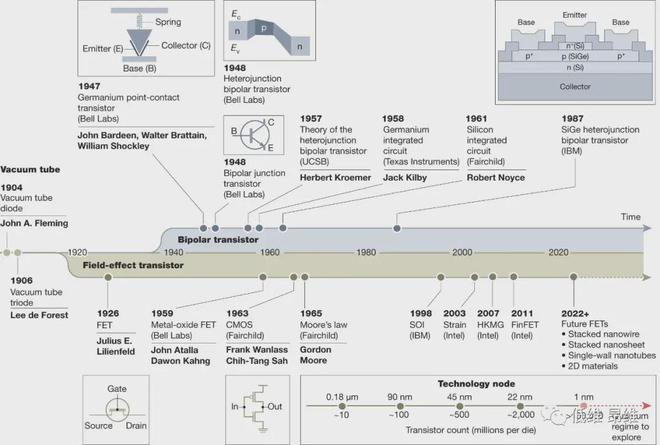

晶体管作为现代信息技术的基石,其发展历史充满了曲折和令人瞩目的突破。自20世纪中叶以来,晶体管的演变从最初的概念到如今的高度集成化,见证了人类创新和科技进步的壮丽历程。

晶体管的发展历史可以追溯到1947年,当时贝尔实验室的三位科学家巴丁(John Bardeen)、布拉丹(Walter Brattain)和肖克利(William Shockley)合作成功地发明了第一台固态三极管,这也被认为是第一个晶体管。这项创新突破了真空管的局限性,开创了半导体器件的时代。不久之后,肖克利还于1956年获得了诺贝尔物理学奖,以表彰他对半导体理论的贡献。

20世纪50年代和60年代,晶体管技术取得了飞速的发展。第一代晶体管广泛应用于计算机和通信设备中,但其体积庞大,能效不高,限制了电子设备的进一步发展。随着集成电路的兴起,晶体管的尺寸开始缩小,从而使电子设备更加紧凑和高效。

1971年,英特尔公司的创始人之一戈登·摩尔提出了“摩尔定律”,预测每隔约18至24个月,集成电路上的晶体管数量将翻倍,同时芯片的成本将减半。这一定律推动了晶体管技术的持续发展,也催生了现代信息技术的蓬勃发展。

随着时间的推移,晶体管尺寸不断缩小,集成度不断提高。20世纪80年代,随着CMOS(互补金属氧化物半导体)技术的引入,电子器件的功耗大幅降低,性能得到显著提升。20世纪90年代,晶体管的微细化和制造工艺的不断改进,使得个人电脑、移动电话等设备的性能急剧提升,同时价格逐渐降低,大众化的信息技术时代由此开启。

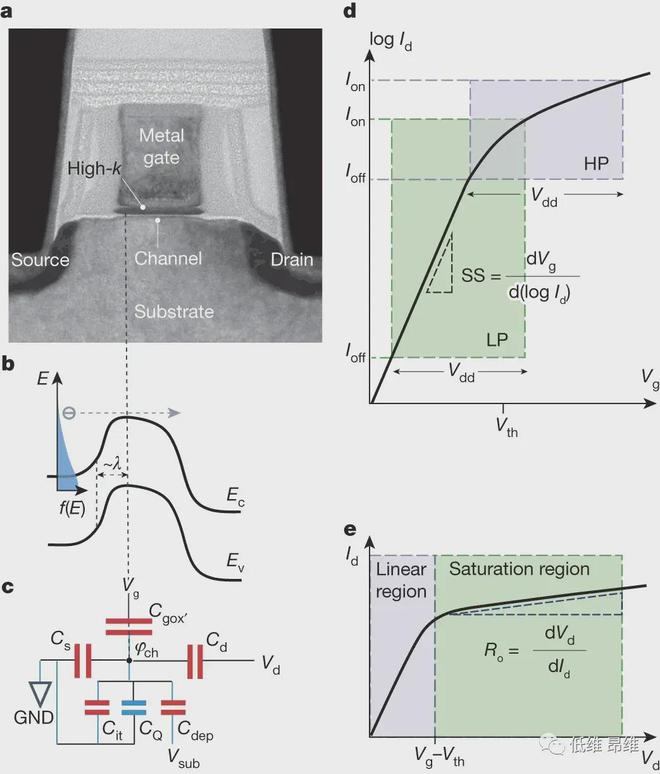

为了分析晶体管的未来,需要先从基本的物理和操作原理开始,了解场效应晶体管(FET)的工作方式以及它在现代技术中的重要性。FET是一种半导体器件,其操作是基于电场调制的,它已经成为现代集成电路的核心组成部分。理解FET的工作原理对于展望晶体管未来的发展具有关键意义。

在FET中,电子流动的控制通过在半导体材料上施加电场来实现。最常见的FET类型是金属-氧化物-半导体场效应晶体管(MOSFET)。MOSFET的结构由金属-氧化物-半导体构成,其中金属电极充当门极,氧化物层作为绝缘层,半导体为通道。通常,MOSFET中的半导体是硅,而氧化物层则是氧化硅。

MOSFET的基本原理是通过调制通道中的电子浓度来控制电流的流动。当在门极施加电压时,电场会影响半导体中的电子,从而调整电子的浓度。这个电场效应导致半导体通道的电导率发生变化,从而控制从源极到漏极的电流流动。通过改变门电压的大小和极性,我们可以实现电流的开关控制,从而实现信息的存储和处理。

然而,随着MOSFET尺寸的不断缩小,晶体管面临着一系列严峻的挑战。这些挑战不仅来自尺寸效应的加剧,还涉及到多个方面的复杂问题。

首先,随着晶体管尺寸的减小,一些不良影响变得更加显著,从而限制了晶体管的性能和能效。其中之一是漏极效应,即源漏电流的泄漏现象。随着尺寸减小,电子在通道中的流动受到限制,从而导致漏极效应的增加。这不仅影响了晶体管的开关速度,还可能导致电流不稳定,从而影响了器件的可靠性和一致性。

其次,寄生电阻和电容的增加也对晶体管的性能产生了影响。随着晶体管尺寸减小,与之相连的电极、源漏区域等的尺寸也随之缩小,导致寄生电阻增加。这使得电流在器件中的传输变得更加复杂,限制了晶体管的响应速度和电流驱动能力。此外,寄生电容的增加也影响了晶体管的高频性能,导致信号衰减和噪声增加,从而影响了信息的传输质量。泄漏电流的增加也是晶体管面临的挑战之一。随着晶体管尺寸的缩小,泄漏电流在器件中的占比逐渐增加,从而导致功耗的增加。泄漏电流不仅浪费能量,还会导致器件的发热问题,影响其可靠性和寿命。

此外,晶体管的制造难度和成本也在逐渐增加,制约了其进一步的发展。随着尺寸的缩小,制造过程变得更加复杂,需要更高精度的工艺和设备。同时,新的材料和器件结构的引入也增加了制造的复杂性。这不仅增加了制造的成本,还可能导致制造过程中的不稳定性和变异性,影响了器件的一致性和可靠性。龙8long8唯一官方网站

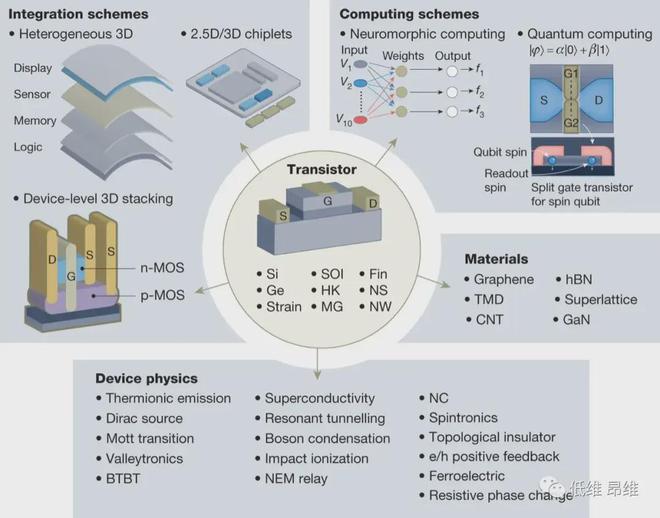

首先,一个引人注目的方向是新的器件结构和材料的出现,以实现更高的性能和能效。负电容场效应晶体管(Negative Capacitance FET,简称NC FET)是一个具有巨大潜力的技术,它利用铁电材料的负电容特性,可以突破传统晶体管电阻的限制,实现更高效的电荷控制。通过在通道材料上引入铁电薄膜,NC FET可以实现比传统MOSFET更小的次阈值摆幅,从而大幅提高性能。另外,悬浮门场效应晶体管(Suspended Gate FET)和Mott相变材料门控晶体管(Mott-G FET)通过引入新的器件结构和相变材料,实现了更小的亚阈值摆幅和更高的电流密度。这些创新性的器件结构和材料将为晶体管的未来发展带来新的可能性long8唯一官方网站,助力计算机技术的飞速进步。

其次,三维集成技术将成为晶体管未来发展的重要方向。传统上,晶体管在平面上布局,但随着技术的发展,垂直堆叠的概念变得愈发重要。通过垂直堆叠不仅可以实现更高的器件集成密度,还可以减少电路互连的长度,从而降低功耗和延迟。三维集成技术的引入不仅可以提供更多的计算资源,还可以为信息技术领域带来新的可能性long8唯一官方网站。例如,三维堆叠的存储器和处理器单元可以更紧密地连接,从而加速数据传输和处理,推动计算机技术的飞速发展。此外,三维集成技术还可以为物联网、人工智能和大数据等领域提供更强大的计算能力,推动科技创新的边界。

除了以上方面,晶体管的未来还将涉及到新的计算范式和技术。神经形态计算和量子计算等新型计算方法正在逐渐崭露头角,它们将彻底改变传统计算机的工作方式和局限性。神经形态计算模仿了人脑的工作原理,通过模拟神经元之间的连接和相互作用,实现高效的模式识别和学习。量子计算则利用量子位(Qubit)的叠加和纠缠特性,实现了在传统计算机难以解决的问题上的突破。这些新型计算方法对晶体管的性能和能效提出了更高的要求,推动了晶体管技术的进一步发展。通过优化晶体管的设计和材料选择,我们有望为神经形态计算和量子计算等领域提供更加强大和高效的计算平台。

综上所述,晶体管的未来充满了令人振奋的机遇和前景。通过不断的创新和技术突破,我们可以期待看到新型器件结构、先进材料和三维集成技术的引入,以及新型计算范式的崭露头角。这些发展将不仅推动信息技术领域的发展,还将影响到医疗、通信、能源、科学和工程等多个领域。未来科学家和工程师的不断创新将为晶体管的未来发展提供不竭的动力,继续为人类创造更加美好的未来。

地址:宁波市鄞州区中钟公庙街道天童北路1393号322室 Copyright © 2012-2023龙8-long8唯一官方网站 版权所有

ICP备案编号:辽ICP备14525020号